## In VLSI & EMBEDDED SYSTEMS

# ACADEMIC REGULATIONS, COURSE COVERAGE SUMMARY & QUESTION BANK

**Department of Electronics and Communication Engineering**

#### **MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY**

(Autonomous Institution – UGC, Govt. of India)

**Sponsored by CMR Educational Society**

(Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NAAC – 'A' Grade - ISO 9001:2015 Certified)

Maisammaguda, Dhulapally, Kompally, Secunderabad – 500100, Telangana State, India.

Contact Number: 7207034237, 9133555162, E-Mail ID: <a href="mailto:mrcet2004@gmail.com">mrcet2004@gmail.com</a>, website: <a href="mailto:www.mrcet.ac.in">www.mrcet.ac.in</a>

#### Vision

To evolve into a center of excellence in Engineering Technology through creative and innovative practices in teaching-learning, promoting academic achievement & research excellence to produce internationally accepted competitive and world class professionals.

#### **Mission**

To provide high quality academic programmes, training activities, research facilities and opportunities supported by continuous industry institute interaction aimed at employability, entrepreneurship, leadership and research aptitude among students.

#### **Quality Policy**

Impart up-to-date knowledge to the students in Electronics & Communication area to make them quality engineers.

Make the students experience the applications on quality equipment and tools. Provide systems, resources and training opportunities to achieve continuous improvement. Maintain global standards in education, training and services.

#### **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

#### M.TECH – VLSI & EMBEDDED SYSTEMS

#### **COURSE STRUCTURE**

#### I Year I Semester

| S.NO. | SUBJECT<br>CODE                  | SUBJECT                                                                                                        | L  | T/<br>P/ | С  | MAX | MARKS |

|-------|----------------------------------|----------------------------------------------------------------------------------------------------------------|----|----------|----|-----|-------|

|       | CODE                             |                                                                                                                |    | D        |    | INT | EXT   |

| 1     | R18D6801                         | VLSI Technology & Design                                                                                       | 3  | -        | 3  | 30  | 70    |

| 2     | R18D6802                         | CPLD & FPGA Architectures& Applications                                                                        | 3  | -        | 3  | 30  | 70    |

| 3     | R18D6803                         | Embedded System design                                                                                         | 3  | -        | 3  | 30  | 70    |

| 4     | R18D6807<br>R18D6808<br>R18D6809 | 1.VLSI Signal Processing 2.CMOS Analog Integrated Circuit Design 3.Programming Languages for Embedded Software | 3  | -        | 3  | 30  | 70    |

| 5     | R18D6810<br>R18D6811<br>R18D6812 | 1.CMOS Digital Integrated Circuit design 2.CAD of Digital System 3.System Design with Embedded Linux           | 3  | -        | 3  | 30  | 70    |

| 6     | OE I                             | OPEN ELECTIVE –I                                                                                               | 3  | -        | 3  | 30  | 70    |

| 7     | R18D6881                         | VLSI Lab                                                                                                       | -  | 3        | 2  | 30  | 70    |

| 8     | R18DHS54                         | Audit Course I - Value Education                                                                               | 2  | -        | -  | 50  | -     |

|       |                                  | Total                                                                                                          | 20 | 3        | 20 | 260 | 490   |

<sup>\*</sup>Audit course: Non-credit course, 50% of scoring is required for the award of the degree

|              | OPEN ELECTIVE I                  |  |  |  |

|--------------|----------------------------------|--|--|--|

| Subject Code | Subject Name                     |  |  |  |

| R18DME51     | Non-Conventional Energy Sources  |  |  |  |

| R18DME52     | Industrial Safety                |  |  |  |

| R18DME53     | Operations Research              |  |  |  |

| R18DHS51     | Business Analytics               |  |  |  |

| R18DCS51     | Scripting Languages              |  |  |  |

| R18DAE51     | Mathematical Modeling Techniques |  |  |  |

| R18DEC51     | Embedded Systems Programming     |  |  |  |

#### I Year II Semester

| S.NO. | SUBJECT  | SUBJECT                              | L | T/P/D | С | MAX | MARKS |

|-------|----------|--------------------------------------|---|-------|---|-----|-------|

|       | CODE     |                                      |   |       |   | INT | EXT   |

| 1     | R18D6804 | Embedded Real Time Operating Systems | 3 | -     | 3 | 30  | 70    |

| 2     | R18D6805 | CMOS Mixed Signal Circuit Design     | 3 | -     | 3 | 30  | 70    |

| 3     | R18D6806 | Low Power VLSI Design                | 3 | -     | 3 | 30  | 70    |

|       |          | ELECTIVE – III                       |   |       |   |     |       |

| 4     | R18D6813 | 1.Adhoc –Wireless Networks           | 3 | _     | 3 | 30  | 70    |

| •     | R18D6814 | 2.SOC Design                         | 3 | _     | 3 | 30  | 70    |

|       | R18D6815 | 3.Memory Technologies                |   |       |   |     |       |

|       |          | ELECTIVE- IV                         |   |       |   |     |       |

|       | R18D6816 | 1.Physical Design Automation         |   |       |   |     |       |

| 5     | R18D6817 | 2.Communication Buses and Interfaces | 3 | -     | 3 | 30  | 70    |

|       | R18D6818 | 3.Multimedia Signal Coding           |   |       |   |     |       |

|       |          |                                      |   |       |   |     |       |

| 6     | OE II    | OPEN ELECTIVE- II                    | 3 | -     | 3 | 30  | 70    |

| 7 | R18D6882 | Embedded Systems Lab                                    | -  | 3 | 2  | 30  | 70  |

|---|----------|---------------------------------------------------------|----|---|----|-----|-----|

| 8 | R18DHS55 | Audit Course II - English for Research Paper<br>Writing | 2  | - | -  | 50  |     |

|   |          | Total                                                   | 20 | 3 | 20 | 260 | 490 |

<sup>\*</sup>Audit course: Non-credit course, 50% of scoring is required for the award of the degree

|              | OPEN ELECTIVE II                        |  |  |  |  |

|--------------|-----------------------------------------|--|--|--|--|

| Subject Code | Subject Name                            |  |  |  |  |

| R18DME54     | Composite Materials                     |  |  |  |  |

| R18DME55     | Waste to Energy                         |  |  |  |  |

| R18DME56     | Industrial Management                   |  |  |  |  |

| R18DHS52     | Cost Management of Engineering Projects |  |  |  |  |

| R18DCS52     | Information Security                    |  |  |  |  |

| R18DAE52     | Unmanned Aerial Vehicles                |  |  |  |  |

| R18DEC52     | Research Methodology                    |  |  |  |  |

#### II Year I Semester

| S.NO. | SUBJECT  | SUBJECT          | L | T/P/D | С  | MAX | MARKS |

|-------|----------|------------------|---|-------|----|-----|-------|

|       | CODE     |                  |   |       |    | INT | EXT   |

|       |          |                  |   |       |    |     |       |

| 1     | R18D6883 | Seminar-I        | - | -     | 2  | 50  | -     |

| 2     | R18D6891 | Mini Project     | - | -     | 4  | 100 | -     |

| 3     | R18D6892 | Project Review-I | • | -     | 8  | 100 | -     |

|       |          | Total            | - | -     | 14 | 250 | -     |

#### II Year II Semester

| S.NO. | SUBJECT  | SUBJECT           | L | T/P/D | С  | MAX | MARKS |

|-------|----------|-------------------|---|-------|----|-----|-------|

|       | CODE     |                   |   |       |    | INT | EXT   |

| 1     | R18D6884 | Seminar-II        | - | -     | 2  | 50  | -     |

| 2     | R18D6893 | Project Review-II | - | -     | 8  | 100 | -     |

| 3     | R18D6894 | Project Viva-voce | - | -     | 8  | -   | 100   |

|       |          | Total             | - | 1     | 18 | 150 | 100   |

#### (R18D6801) VLSI TECHNOLOGY AND DESIGN

#### UNIT -I:

#### **Review of Microelectronics and Introduction to MOS Technologies:**

MOS, CMOS, BiCMOS Technology, Basic Electrical Properties of MOS, CMOS &BiCMOS Circuits:  $I_{ds}$  – $V_{ds}$  relationships, ThresholdVoltage V T ,  $g_m$  ,  $g_{ds}$  and  $\omega_o$  , Pass Transistor, MOS, CMOS & Bi CMOS Inverters,  $Z_{pu}$  / $Z_{pd}$  , MOS Transistor circuit model, Latch-up in CMOS circuits.

#### UNIT -II:

#### **Layout Design and Tools:**

Transistor structures, Wires and Vias, Scalable Design rules, Layout Design tools.

#### **Logic Gates & Layouts:**

Static Complementary Gates, Switch Logic, Alternative Gate circuits, Low power gates, Resistive and Inductive interconnect delays.

#### UNIT -III:

#### **Combinational Logic Networks:**

Layouts, Simulation, Network delay, Interconnect design, Power optimization, Switch logic networks, Gate and Network testing.

#### UNIT-IV:

#### **Sequential Systems:**

Memory cells and Arrays, Clocking disciplines, Design, Power optimization, Design validation andtesting.

#### UNIT -V:

#### Floor Planning:

Floor planning methods, Global Interconnect, Floor Plan Design, Off-chip connections.

#### **TEXT BOOKS:**

1. Essentials of VLSI Circuits and Systems, K. Eshraghian Eshraghian. D, A. Pucknell, 2005,

| PHI  | l.                                                                                                |

|------|---------------------------------------------------------------------------------------------------|

| 2. N | Modern VLSI Design – Wayne Wolf, 3 rd Ed., 1997, Pearson Education.                               |

| REF  | FERENCE BOOKS:                                                                                    |

| 1. I | ntroduction to VLSI Systems: A Logic, Circuit and System Perspective – Ming-BO Lin, CRC           |

| Pre  | ess, 2011.                                                                                        |

| 2. F | Principals of CMOS VLSI Design – N.H.E Weste, K. Eshraghian, 2 <sup>nd</sup> Ed., Addison Wesley. |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

|      |                                                                                                   |

#### (R18D6802) CPLD AND FPGA ARCHITECURES AND APPLICATIONS

#### **UNIT-I:**

#### **Introduction to Programmable Logic Devices:**

Introduction, Simple Programmable Logic Devices – Read Only Memories, Programmable Logic Arrays, Programmable Array Logic, Programmable Logic Devices/Generic Array Logic; Complex

Programmable Logic Devices – Architecture of Xilinx Cool Runner XCR3064XL CPLD, CPLD

Implementation of a Parallel Adder with Accumulation

#### UNIT-II:

#### **Field Programmable Gate Arrays:**

Organization of FPGAs, FPGA Programming Technologies, Programmable Logic Block Architectures, Programmable Interconnects, Programmable I/O blocks in FPGAs, Dedicated Specialized Components of FPGAs, Applications of FPGAs.

#### UNIT -III:

#### **SRAM Programmable FPGAs:**

Introduction, Programming Technology, Device Architecture, The Xilinx XC2000, XC3000 and XC4000 Architectures.

#### UNIT -IV:

#### **Anti-Fuse Programmed FPGAs:**

Introduction, Programming Technology, Device Architecture, The Actel ACT1, ACT2 and ACT3 Architectures.

#### UNIT -V:

#### **Design Applications:**

General Design Issues, Counter Examples, A Fast Video Controller, A Position Tracker for a Robot Manipulator, A Fast DMA Controller, Designing Counters with ACT devices, Designing Adders and Accumulators with the ACT Architecture.

#### **TEXT BOOKS:**

- 1. Field Programmable Gate Array Technology Stephen M. Trimberger, Springer International Edition.

- 2. Digital Systems Design Charles H. Roth Jr, Lizy Kurian John, Cengage Learning.

- 1. Field Programmable Gate Arrays John V. Oldfield, Richard C. Dorf, Wiley India.

- 2. Digital Design Using Field Programmable Gate Arrays Pak K. Chan/Samiha Mourad, Pearson Low Price Edition.

- 3. Digital Systems Design with FPGAs and CPLDs Ian Grout, Elsevier, Newnes.

- 4. FPGA based System Design Wayne Wolf, Prentice Hall Modern Semiconductor Design Series.

#### (R18D6803) EMBEDDED SYSTEM DESIGN

#### UNIT -I:

#### **ARM Architecture:**

ARM Design Philosophy, Registers, Program Status Register, Instruction Pipeline, Interrupts and Vector Table, Architecture Revision, ARM Processor Families.

#### UNIT -II:

#### **ARM Programming Model – I:**

Instruction Set: Data Processing Instructions, Addressing Modes, Branch, Load, Store Instructions,

PSR Instructions, Conditional Instructions.

#### UNIT -III:

#### **ARM Programming Model – II:**

Thumb Instruction Set: Register Usage, Other Branch Instructions, Data Processing Instructions,

Single-Register and Multi Register Load-Store Instructions, Stack, Software Interrupt Instructions

#### UNIT-IV:

#### **ARM Programming:**

Simple C Programs using Function Calls, Pointers, Structures, Integer and Floating Point Arithmetic, Assembly Code using Instruction Scheduling, Register Allocation, Conditional Execution and Loops.

#### UNIT -V:

#### **Memory Management:**

Cache Architecture, Polices, Flushing and Caches, MMU, Page Tables, Translation, Access Permissions, Context Switch.

#### **TEXT BOOKS:**

- 1. ARM Systems Developer's Guides- Designing & Optimizing System Software Andrew N. Sloss, Dominic Symes, Chris Wright, 2008, Elsevier.

- 2. Professional Embedded ARM development-James A Langbridge, Wiley/Wrox

- 1. Embedded Microcomputer Systems, Real Time Interfacing Jonathan W. Valvano Brookes / Cole, 1999, Thomas Learning.

- 2. ARM System on Chip Architecture, Steve Furber, 2<sup>nd</sup> Edition, Pearson

#### (R18D6807) VLSI SIGNAL PROCESSING

(ELECTIVE-I)

#### UNIT I:

#### Introduction To DSP Systems, Pipelining And Parallel Processing Of FIR Filters

Introduction to DSP systems – Typical DSP algorithms, Data flow and Dependence graphs - critical path, Loop bound, iteration bound, Longest path matrix algorithm,

Pipelining and Parallel processing of FIR filters, Pipelining and Parallel processing for low power.

#### UNIT II:

#### **Retiming, Algorithmic Strength Reduction**

Retiming – definitions and properties, Unfolding – an algorithm for unfolding, properties of unfolding, sample period reduction and parallel processing application, Algorithmic strength reduction in filters and transforms – 2-parallel FIR filter, 2-parallel fast FIR filter, DCT architecture, rank-order filters, Odd-Even merge-sort architecture, parallel rank-order filters.

#### **UNIT III:**

#### Fast Convolution, Pipelining and Parallel Processing Of IIR Filters

Fast convolution – Cook-Toom algorithm, modified Cook-Toom algorithm, Pipelined and parallel recursive filters – Look-Ahead pipelining in first-order IIR filters, Look-Ahead pipelining with power-of-2 decomposition, Clustered look-ahead pipelining, Parallel processing of IIR filters, combined pipelining and parallel processing of IIR filters.

#### **UNIT IV:**

#### **Bit-Level Arithmetic Architectures**

Bit-level arithmetic architectures – parallel multipliers with sign extension, parallel carry-ripple and carry-save multipliers, Design of Lyon's bit-serial multipliers using Horner's rule, bit-serial FIR filter, CSD representation, CSD multiplication using Horner's rule for precision improvement, Distributed Arithmetic fundamentals and FIR filters

#### **UNIT V:**

#### Numerical Strength Reduction, Synchronous, Wave and Asynchronous Pipelining

Numerical strength reduction – subexpression elimination, multiple constant multiplication, iterative matching, synchronous pipelining and clocking styles, clock skew in edge-triggered single phase clocking, two-phase clocking, wave pipelining. Asynchronous pipelining bundled data versus dual rail protocol.

#### **REFERENCES:**

- 1. Keshab K. Parhi, "VLSI Digital Signal Processing Systems, Design and implementation", Wiley, Interscience, 2007.

- 2. U. Meyer Baese, "Digital Signal Processing with Field Programmable Gate Arrays", Springer, Second Edition, 2004

- 3. Mohammad Isamail and Terri Fiez, Analog VLSI signal and information processing,

McGraw Hill, 1994

#### (R18D6808) CMOS ANALOG INTEGRATED CIRCUIT DESIGN

#### (ELECTIVE-I)

#### **UNIT -I: MOS Devices and Modeling:**

The MOS Transistor, Passive Components- Capacitor & Resistor, Integrated circuit Layout, CMOSDevice Modeling - Simple MOS Large-Signal Model, Other Model Parameters, Small-Signal Model for the MOS Transistor, Computer Simulation Models, Sub-threshold MOS Model.

**UNIT -II: Analog CMOS Sub-Circuits:** MOS Switch, MOS Diode, MOS Active Resistor, Current Sinks and Sources, Current Mirrors-Currentmirror with Beta Helper, Degeneration, Cascode current Mirror and Wilson Current Mirror, Current and Voltage References, Band gap Reference.

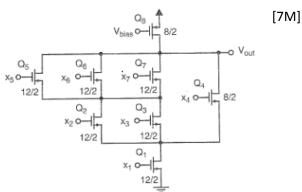

**UNIT -III: CMOS Amplifiers:** Inverters, Differential Amplifiers, Cascode Amplifiers, Current Amplifiers, Output Amplifiers, High Gain Amplifiers Architectures.

**UNIT -IV: CMOS Operational Amplifiers:** Design of CMOS Op Amps, Compensation of Op Amps, Design of Two-Stage Op Amps, Power-Supply Rejection Ratio of Two-Stage Op Amps, Cascode Op Amps, Measurement Techniques of OPAmp.

**UNIT -V: Comparators:** Characterization of Comparator, Two-Stage, Open-Loop Comparators, Other Open-Loop Comparators, Improving the Performance of Open-Loop Comparators, Discrete-Time Comparators.

#### **TEXT BOOKS:**

- 1. CMOS Analog Circuit Design Philip E. Allen and Douglas R. Holberg, Oxford University Press, International Second Edition/Indian Edition, 2010.

- 2. Analysis and Design of Analog Integrated Circuits- Paul R. Gray, Paul J. Hurst, S. Lewis and

- R. G. Meyer, Wiley India, Fifth Edition, 2010.

- 1. Analog Integrated Circuit Design- David A. Johns, Ken Martin, Wiley Student Edn, 2013.

- 2. Design of Analog CMOS Integrated Circuits- Behzad Razavi, TMH Edition.

- 3. CMOS: Circuit Design, Layout and Simulation- Baker, Li

#### (R18D6809) PROGRAMMING LANGUAGES FOR EMBEDDED SOFTWARE

(ELECTIVE-I)

#### UNIT I:

#### **Embedded 'C' Programming**

Bitwise operations, Dynamic memory allocation, OS services, Linked stack and queue, Sparse matrices, Binary tree, Interrupt handling in C, Code optimization issues, Writing LCD drives, LED drivers, Drivers for serial port communication, Embedded Software Development Cycle and Methods (Waterfall, Agile)

#### UNITII:

#### **Object Oriented Programming**

Introduction to procedural, modular, object-oriented and generic programming techniques,

Limitations of procedural programming, objects, classes, data members, methods, data encapsulation, data abstraction and information hiding, inheritance, polymorphism

#### **UNIT III:**

#### **CPP Programming**

'cin', 'cout', formatting and I/O manipulators, new and delete operators, Defining a class, data members and methods, 'this' pointer, constructors, destructors, friend function, dynamic memory allocation

#### **UNIT IV:**

#### **Overloading, Inheritance & Templates**

Need of operator overloading, overloading the assignment, overloading using friends, type conversions, single inheritance, base and derived classes, friend classes, types of inheritance, hybrid inheritance, multiple inheritance, virtual base class, polymorphism, virtual functions

#### **Templates**

Function template and class template, member function templates and template arguments, Exception Handling: syntax for exception handling code: try-catch-throw,

Multiple Exceptions.

#### **UNIT V:**

#### **Scripting Languages**

Overview of Scripting Languages – PERL, CGI, VB Script, Java Script, PERL: Operators, Statements Pattern Matching etc. Data Structures, Modules, Objects, Tied Variables, Inter process Communication Threads, Compilation & Line Interfacing.

#### **TEXT BOOKS:**

- 1. Michael J. Pont, "Embedded C", Pearson Education, 2nd Edition, 2008

- 2. Randal L. Schwartz, "Learning Perl", O'Reilly Publications, 6th Edition 2011

- 3. A. Michael Berman, "Data structures via C++", Oxford University Press, 2002

- 4. Robert Sedgewick, "Algorithms in C++", Addison Wesley Publishing Company, 1999

- 5. Abraham Silberschatz, Peter B, Greg Gagne, "Operating System Concepts", John Willey

- & Sons, 2005

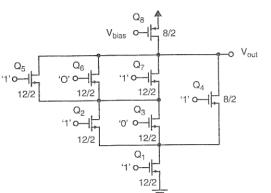

#### (R18D6810) CMOS DIGITAL INTEGRATED CIRCUIT DESIGN

(ELECTIVE-II)

#### UNIT -I:

#### **MOS Design:**

Pseudo NMOS Logic – Inverter, Inverter threshold voltage, Output high voltage, Output Low voltage, Gain at gate threshold voltage, Transient response, Rise time, Fall time, Pseudo NMOS logic gates, Transistor equivalency, CMOS Inverter logic.

#### UNIT -II:

#### **Combinational MOS Logic Circuits:**

MOS logic circuits with NMOS loads, Primitive CMOS logic gates – NOR & NAND gate, ComplexLogic circuits design – Realizing Boolean expressions using NMOS gates and CMOS gates , AOI andOIA gates, CMOS full adder, CMOS transmission gates, Designing with Transmission gates.

#### UNIT -III:

#### **Sequential MOS Logic Circuits:**

Behavior of bistable elements, SR Latch, Clocked latch and flip flop circuits, CMOS D latch and edgetriggered flipflop.

#### UNIT -IV:

#### **Dynamic Logic Circuits:**

Basic principle, Voltage Bootstrapping, Synchronous dynamic pass transistor circuits, Dynamic CMOStransmission gate logic, High performance Dynamic CMOS circuits.

#### UNIT -V:

#### **Semiconductor Memories:**

Types, RAM array organization, DRAM – Types, Operation, Leakage currents in DRAM cell andrefresh operation, SRAM operation Leakage currents in SRAM cells, Flash Memory- NOR flash and NAND flash.

#### **TEXT BOOKS:**

- 1. Digital Integrated Circuit Design Ken Martin, Oxford University Press, 2011.

- 2. CMOS Digital Integrated Circuits Analysis and Design Sung-Mo Kang, Yusuf Leblebici,

#### **REFERENCE BOOKS:**

TMH, 3 rd Ed., 2011.

- Introduction to VLSI Systems: A Logic, Circuit and System Perspective Ming-BO Lin, CRC

Press, 2011

- 2. Digital Integrated Circuits A Design Perspective, Jan M. Rabaey, AnanthaChandrakasan, Borivoje Nikolic, 2 nd Ed., PHI.

#### (R18D6811)CAD OF DIGITAL SYSTEM

(ELECTIVE-II)

#### **UNIT I:**

#### **VLSI Design Methodologies**

Introduction to VLSI Design methodologies - Review of Data structures and algorithms - Review of VLSI Design automation tools - Algorithmic Graph Theory and Computational Complexity - Tractable and Intractable problems - general purpose methods for combinatorial optimization.

#### **UNIT II**

#### **Design Rules**

Layout Compaction - Design rules - problem formulation - algorithms for constraint graph compaction - placement and partitioning - Circuit representation - Placement algorithms - partitioning

#### **UNIT III:**

#### **Floor Planning**

Floor planning concepts - shape functions and floorplan sizing - Types of local routing problems - Area routing - channel routing - global routing - algorithms for global routing.

#### **UNIT IV:**

#### Simulation

Simulation - Gate-level modeling and simulation - Switch-level modeling and simulation - Combinational Logic Synthesis - Binary Decision Diagrams - Two Level Logic Synthesis.

#### **UNIT V:**

#### **Modelling And Synthesis**

High level Synthesis - Hardware models - Internal representation - Allocation assignment and scheduling - Simple scheduling algorithm - Assignment problem - High level transformations.

#### **TEXT BOOKS:**

1. S.H. Gerez, "Algorithms for VLSI Design Automation", John Wiley & Sons, 2002. 2. N.A. Sherwani, "Algorithms for VLSI Physical Design Automation", Kluwer Academic Publishers, 2002.

#### (R18D6812)SYSTEM DESIGN WITH EMBEDDED LINUX

(ELECTIVE-II)

#### **UNIT I: Embedded OS (Linux) Internals**

Linux internals: Process Management, File Management, Memory Management, I/O Management. Overview of POSIX APIs, Threads — Creation, Cancellation, POSIX Threads Inter Process Communication - Semaphore, Pipes, FIFO, Shared Memory Kernel: Structure, Kernel Module Programming Schedulers and types of scheduling.

Interfacing: Serial, Parallel Interrupt Handling Linux Device Drivers: Character, USB, Block & Network

#### **UNIT II: Open source RTOS**

Basics of RTOS: Real-time concepts, Hard Real time and Soft Real-time, Differences between General Purpose OS & RTOS, Basic architecture of an RTOS, Scheduling Systems, Inter-process communication, Performance Metric in scheduling models, Interrupt management in RTOS environment, Memory management, File systems, I/O Systems, Advantage and disadvantage of RTOS.

#### **UNIT III: Open Source RTOS Issues**

POSIX standards, RTOS Issues - Selecting a Real Time Operating System, RTOS comparative study. Converting a normal Linux kernel to real time kernel, Xenomai basics, Overview of Open source RTOS for Embedded systems (Free RTOS/ Chibios-RT) and application development.

#### **UNIT IV: VxWorks / Free RTOS**

VxWorks/ Free RTOS Scheduling and Task Management - Realtime scheduling, Task Creation, Intertask Communication, Pipes, Semaphore, Message Queue, Signals, Sockets, Interrupts I/O Systems - General Architecture, Device Driver Studies, Driver Module explanation, Implementation of Device Driver for a peripheral

#### **UNIT V: Case study**

Cross compilers, debugging Techniques, Creation of binaries & porting stages for Embedded Development board (Beagle Bone Black, Rpi or similar), Porting an Embedded OS/ RTOS to a target board (). Testing a real time application on the board

#### **TEXT BOOKS:**

- 1. Essential Linux Device Drivers, Venkateswaran Sreekrishnan

- 2. Writing Linux Device Drivers: A Guide with Exercises, J. Cooperstein

- 3. Real Time Concepts for Embedded Systems Qing Li, Elsevier

- 1. Embedded Systems Architecture Programming and Design: Raj Kamal, Tata McGraw Hill

- 2. Embedded/Real Time Systems Concepts, Design and Programming Black Book, Prasad, KVK

- 3. Software Design for Real-Time Systems: Cooling, J E Proceedings of 17the IEEE Real-Time Systems Symposium December 4-6, 1996 Washington, DC: IEEE Computer Society

- 4. Real-time Systems Jane Liu, PH 2000

- 5. Real-Time Systems Design and Analysis: An Engineer's Handbook: Laplante, Phillip A

- 6. Structured Development for Real Time Systems V1 : Introduction and Tools: Ward, Paul T & Mellor, Stephen J

- 7. Structured Development for Real Time Systems V2 : Essential Modeling Techniques: Ward, Paul T & Mellor, Stephen J

- 8. Structured Development for Real Time Systems V3 : Implementation Modeling Techniques: Ward, Paul T & Mellor, Stephen J

- 9. Monitoring and Debugging of Distributed Real-Time Systems: TSAI, Jeffrey J P & Yang, J H

- 10. Embedded Software Primer: Simon, David E.

- 11. Embedded Systems Architecture Programming and Design: Raj Kamal, Tata McGraw Hill

#### (R18DME51) NON-CONVENTIONAL ENERGY SOURCES

#### (OPEN ELECTIVE-I)

#### UNIT-I

**Introduction**: Energy Scenario, Survey of energy resources. Classification and need for conventional energy resources.

**Solar Energy:** The Sun-sun-Earth relationship, Basic matter to waste heat energy circuit, SolarRadiation, Attention, Radiation measuring instruments.

**Solar Energy Applications:** Solar water heating. Space heating, Active and passive heating, Energystorage, Selective surface, Solar stills and ponds, solar refrigeration, Photovoltaic generation.

#### **UNIT-II**

**Geothermal Energy:** Structure of earth, Geothermal Regions, Hot springs. Hot Rocks, HotAquifers. Analytical methods to estimate thermal potential. Harnessing techniques, Electricity generating systems.

#### UNIT-III

**Direct Energy Conversion:** Nuclear Fusion, Fusion reaction, P-P cycle, Carbon cycle, Deuterium cycle, Condition for controlled fusion, Fuel cells and photovoltaic, Thermionic and Thermoelectric generation and MHD generator.

**Hydrogen Gas as Fuel:** Production methods, Properties, I.C. Engines applications, Utilization strategy, Performances.

#### **UNIT-IV**

**Bioenergy:** Biomass energy sources. Plant productivity, Biomass wastes, aerobic and anaerobicbioconversion processes, Raw material and properties of bio-gas, Bio-gas plant technology and status, the energetic and economics of biomass systems, Biomass gasification

#### **UNIT-V**

**Wind Energy**: Wind, Beaufort number, Characteristics, Wind energy conversion systems, Types, Betz model. Interference factor. Power coefficient, Torque coefficient and Thrust coefficient, Lift machines and Drag machines. Matching Electricity generation. **Energy from Oceans**: Tidal energy, Tides, Diurnal and semi-diurnal nature, Power from tides, WaveEnergy, Waves, Theoretical energy available. Calculation of period and phase velocity of waves, Wave power systems, submerged devices. Ocean thermal Energy, Principles, Heat exchangers, Pumping requirements, Practical considerations.

#### **TEXTBOOKS:**

- 1. Non-conventional Energy Sources / GD Rai/Khanna publications.

- 2.Non-Conventional Energy Sources and Utilisation (Energy Engineering)/ R KRajput/ S.Chand.

- 3.Renewable Energy Sources /Twidell& Weir/Taylor and Francis/ 2<sup>nd</sup> special Indian edition.

- 1.Renewable Energy Resources- Basic Principles and Applications/ G.N.Tiwari and M.K.GhosalNarosa Publications.

- 2.Renewable Energy Resources/ John Twidell& Tony Weir/Taylor & Francis/2<sup>nd</sup> edition.

- 3.Non Conventional Energy / K.Mittal/ Wheeler.

#### (R18DME52)INDUSTRIAL SAFETY

#### (OPEN ELECTIVE-I)

#### UNIT-I:

#### **Industrial safety**

Accident, causes, types, results and control, mechanical and electrical hazards, types, causes and preventive steps/procedure, describe salient points of factories act 1948 for health and safety, wash rooms, drinking water layouts, light, cleanliness, fire, guarding, pressure vessels, etc, Safety color codes. Fire prevention and firefighting, equipment and methods.

#### **UNIT-II:**

#### **Fundamentals of maintenance engineering**

Definition and aim of maintenance engineering, Primary and secondary functions and responsibility of maintenance department, Types of maintenance, Types and applications of tools used for maintenance, Maintenance cost & its relation with replacement economy, Service life of equipment.

#### UNIT-III:

#### Wear and Corrosion and their prevention

Wear- types, causes, effects, wear reduction methods, lubricants-types and applications, Lubrication methods, general sketch, working and applications, i. Screw down grease cup, ii. Pressure grease gun, iii. Splash lubrication, iv.Gravity lubrication, v. Wick feed lubrication vi. Side feed lubrication, vii. Ring lubrication, Definition, principle and factors affecting the corrosion. Types of corrosion, corrosion prevention methods.

#### **UNIT-IV:**

#### **Fault Tracing**

Fault tracing-concept and importance, decision tree concept, need and applications, sequence of fault finding activities, show as decision tree, draw decision tree for problems in machine tools, hydraulic, pneumatic,automotive, thermal and electrical equipment's like, i. Any one machine tool, ii. Pump iii. Air compressor, iv. Internal combustion engine, v. Boiler, vi. Electrical motors, Types of faults in machine tools and their general causes.

#### UNIT-V:

#### Periodic and preventive maintenance

Periodic inspection-concept and need, degreasing, cleaning and repairing schemes, overhauling of mechanical components, overhauling of electrical motor, common troubles and remedies of electric motor, repair complexities and its use, definition, need, steps and advantages of preventive maintenance. Steps/procedure for periodic and preventive maintenance of: I. Machine tools, ii. Pumps, iii. Air compressors, iv. Diesel generating (DG) sets, Program and schedule of preventive maintenance of mechanical and electrical equipment, advantages of preventive maintenance, Repair cycle concept and importance.

#### **TEXTBOOKS:**

- 1. Maintenance Engineering Handbook, Higgins & Morrow, Da Information Services.

- 2. Maintenance Engineering, H. P. Garg, S. Chand and Company.

- 3. Pump-hydraulic Compressors, Audels, Mcgrew Hill Publication.

- 4. Foundation Engineering Handbook, Winterkorn, Hans, Chapman & Hall London.

#### (R18DME53)OPERATIONS RESEARCH

(OPEN ELECTIVE-I)

#### **UNIT I:**

#### **Introduction to OR & Linear Programming**

Evolution of OR, definition of OR, scope of OR, application areas of OR, steps (phases) in OR study, characteristics and limitations of OR, models used in OR, linear programming (LP) problem-formulation and solution by graphical method.

Solution Of Linear Programming Problems: The simplex method, canonical and standard form of an LP problem, slack, surplus and artificial variables, big M method and concept of duality, dual simplex method.

#### **UNIT II**

#### **Transportation Problem**

Formulation of transportation problem, types, initial basic feasible solution using different methods, optimal solution by MODI method, degeneracy in transportation problems, application of transportation problem concept for maximization cases, Assignment Problem-formulation, types, application to maximization cases and travelling salesman problem.

#### **UNIT III:**

#### **Integer Programming**

Pure and mixed integer programming problems, solution of Integer programming problems-Gomory's all integer cutting plane method and mixed integer method, branch and bound method, Zero-One programming, Pert-CPM Techniques:

Introduction, network construction - rules, Fulkerson's rule for numbering the events, AON and AOA diagrams; Critical path method to find the expected completion time of a project, floats; PERT for finding expected duration of an activity and project, determining the probability of completing a project, predicting the completion time of project; crashing of simple projects.

#### **UNIT IV:**

#### **Queuing Theory**

Queuing systems and their characteristics, Pure-birth and Pure-death models (only equations), empirical queuing models – M/M/1 and M/M/C models and their steady state performance analysis.

#### **UNIT V:**

#### **Game Theory**

Formulation of games, types, solution of games with saddle point, graphical method of solving mixed strategy games, dominance rule for solving mixed strategy games.

**Sequencing:**Basic assumptions, sequencing 'n' jobs on single machine using priority rules, sequencing using Johnson's rule-'n' jobs on two machines, 'n' jobs on three machines, 'n' jobs on 'm' machines. Sequencing two jobs on 'm' machines using graphical method.

#### **TEXTBOOKS**:

- 1. H.A. Taha, Operations Research, An Introduction, PHI, 2008

- 2. H.M. Wagner, Principles of Operations Research, PHI, Delhi, 1982.

- 3. J.C. Pant, Introduction to Optimisation: Operations Research, Jain Brothers, Delhi, 2008

- 4. Hitler Libermann Operations Research: McGraw Hill Pub. 2009

- 5. Pannerselvam, Operations Research: Prentice Hall of India 2010

- 6. Harvey M Wagner, Principles of Operations Research: Prentice Hall of India 2010

#### (R18DHS51) BUSINESS ANALYTICS

(OPEN ELECTIVE - I)

#### **UNIT I:**

#### **Business Analytics**

Overview of Business analytics, Scope of Business analytics, Business Analytics Process, Relationship of Business Analytics Process and organization, competitive advantages of Business Analytics, Statistical Tools: Statistical Notation, Descriptive Statistical methods, Review of probability distribution and data modelling, sampling and estimation methods overview

#### **UNIT II:**

#### **Trendiness and Regression Analysis**

Modelling Relationships and Trends in Data, simple Linear Regression, Important Resources, Business Analytics Personnel, Data and models for Business, analytics, problem solving, Visualizing and Exploring Data, Business Analytics, Technology.

#### UNIT III:

#### **Organization Structures of Business analytics:**

Team management, Management Issues, Designing Information Policy, Outsourcing, Ensuring Data Quality, Measuring contribution of Business analytics, Managing Changes, Descriptive Analytics, predictive analytics, predictive Modelling, Predictive analytics, analysis, Data Mining, Data Mining Methodologies, Prescriptive analytics and its step in the business analytics Process, Prescriptive Modelling, nonlinear Optimization.

#### **UNIT IV:**

#### **Forecasting Techniques**

Qualitative and Judgmental Forecasting, Statistical Forecasting Models, Forecasting Models for Stationary Time Series, Forecasting Models for Time Series with a Linear Trend, Forecasting Time Series with Seasonality, Regression Forecasting with Casual Variables, Selecting Appropriate Forecasting Models.

Monte Carlo Simulation and Risk Analysis: Monte Carle Simulation Using Analytic Solver Platform, New-Product Development Model, Newsvendor Model, Overbooking Model, Cash Budget Model.

#### **UNIT V:**

#### **Decision Analysis**

Formulating Decision Problems, Decision Strategies with the without Outcome Probabilities, Decision Trees, The Value of Information, Utility and Decision Making. Recent Trends in Embedded and collaborative business intelligence, Visual data recovery, Data Storytelling and Data journalism

#### **TEXT BOOKS:**

- 1. Business analytics Principles, Concepts, and Applications by Marc J. Schniederjans, Dara G.Schniederjans, Christopher M. Starkey, Pearson FT Press.

- 2. Business Analytics by James Evans, persons Education.

#### (R18DCS51) Scripting Languages

#### (OPEN ELECTIVE I)

**Objectives:** The course demonstrates an in depth understanding of the tools and the scripting languages necessary for design and development of applications dealing with Bio-information/Bio-data. The instructor is advised to discuss examples in the context of Bio-data/ Bio-information application development.

#### **UNIT I**

Introduction to PERL and Scripting Scripts and Programs, Origin of Scripting, Scripting Today, Characteristics of Scripting Languages, Web Scripting, and the universe of Scripting Languages. PERL- Names and Values, Variables, Scalar Expressions, Control Structures, arrays, list, hashes, strings, pattern and regular expressions, subroutines, advance perl - finer points of looping, pack and unpack, filesystem, eval, data structures, packages, modules, objects, interfacing to the operating system, Creating Internet ware applications, Dirty Hands Internet Programming, security Issues.

#### **UNIT II**

PHP Basics- Features, Embedding PHP Code in your Web pages, Outputting the data to the browser, Datatypes, Variables, Constants, expressions, string interpolation, control structures, Function, Creating a Function, Function Libraries, Arrays, strings and Regular Expressions.

#### **UNIT III**

Advanced PHP Programming Php and Web Forms, Files, PHP Authentication and Methodologies -Hard Coded, File Based, Database Based, IP Based, Login Administration, Uploading Files with PHP, Sending Email using PHP, PHP Encryption Functions, the Mcrypt package, Building Web sites for the World – Translating Websites- Updating Web sites Scripts, Creating the Localization Repository, Translating Files, text, Generate Binary Files, Set the desired language within your scripts, Localizing Dates, Numbers and Times.

#### **UNIT IV**

TCL Structure, syntax, Variables and Data in TCL, Control Flow, Data Structures, input/output, procedures, strings, patterns, files, Advance TCL- eval, source, exec and up level commands, Name spaces, trapping errors, event driven programs, making applications internet aware, Nuts

and Bolts Internet Programming, Security Issues, C Interface. Tk- Visual Tool Kits, Fundamental Concepts of Tk, Tk by example, Events and Binding, Perl-Tk.

#### **UNIT V**

Python Introduction to Python language, python-syntax, statements, functions, Built-infunctions and Methods, Modules in python, Exception Handling, Integrated Web Applications in Python – Building Small, Efficient Python Web Systems, Web Application Framework.

#### **TEXT BOOKS:**

- 1. The World of Scripting Languages, David Barron, Wiley Publications.

- 2. Python Web Programming, Steve Holden and David Beazley, New Riders Publications.

- 3. Beginning PHP and MySQL, 3rd Edition, Jason Gilmore, Apress Publications (Dreamtech)

- 1. Open Source Web Development with LAMP using Linux, Apache, MySQL, Perl and PHP, J.Lee and B.Ware (Addison Wesley) Pearson Education.

- 2. Programming Python, M.Lutz, SPD.

- 3. PHP 6 Fast and Easy Web Development, Julie Meloni and Matt Telles, Cengage Learning Publications.

- 4. PHP 5.1,I.Bayross and S.Shah, The X Team, SPD.

- 5. Core Python Programming, Chun, Pearson Education.

- 6. Guide to Programming with Python, M.Dawson, Cengage Learning.

- 7. Perl by Example, E.Quigley, Pearson Education.

- 8. Programming Perl, Larry Wall, T.Christiansen and J.Orwant, O'Reilly, SPD.

- 9. Tcl and the Tk Tool kit, Ousterhout, Pearson Education.

- 10. PHP and MySQL by Example, E.Quigley, Prentice Hall(Pearson).

- 11. Perl Power, J.P.Flynt, Cengage Learning.

- 12. PHP Programming solutions, V.Vaswani, TMH.

#### (R18DAE51) Mathematical Modeling Techniques

(OPEN ELECTIVE I)

#### **UNIT-I: INTRODUCTION TO MODELING AND SINGULAR PERTURBATION METHODS**

Definition of a model, Procedure of modeling: problem identification, model formulation, reduction, analysis, Computation, model validation, Choosing the model, Singular Perturbations: Elementary boundary layer theory, Matched asymptotic expansions, Inner layers, nonlinear oscillations

#### **UNIT-II: VARIATIONAL PRINCIPLES AND RANDOM SYSTEMS**

Variational calculus: Euler's equation, Integrals and missing variables, Constraints and Lagrange multipliers, Variational problems: Optics-Fermat's principle, Analytical mechanics: Hamilton's principle, Symmetry: Noether's theorem, Rigid body motion, Random systems: Random variables, Stochastic processes, Monte Carlo method

#### UNIT-III: FINITE DIFFERENCES: ORDINARY AND PARTIAL DIFFERENTIAL EQUATIONS

ODE: Numerical approximations, Runge-Kutta methods, Beyond Runge-Kutta, PDE: Hyperbolic equations-waves, Parabolic equations-diffusion, Elliptic equations-boundary values, **CELLULAR AUTOMATA AND LATTICE GASES:** Lattice gases and fluids, Cellular automata and computing

#### **UNIT- IV: FUNCTION FITTING AND TRANSFORMS**

Function fitting: Model estimation, Least squares, Linear least squares: Singular value decomposition, Non-linear least squares: Levenberg-Marquardt method, Estimation, Fisher information, and Cramer-Rao inequality, Transforms:Orthogonal transforms, Fourier transforms, Wavelets, Principal components

**FUNCTION FITTING ARCHITECTURES:**Polynomials: Pade approximants, Splines, Orthogonal functions, Radial basis functions, Over-fitting, Neural networks: Back propagation, Regularization

**UNIT-V**: **OPTIMIZATION AND SEARCH**: Multidimensional search, Local minima, Simulated annealing, Genetic algorithms **FILTERING AND STATE ESTIMATION**: Matched filters, Wiener filters, Kalman filters, Non-linearity and entrainment, Hidden Markov models

#### **TEXT BOOK:**

1. *The Nature of Mathematical Modeling*, Neil Gershenfeld, Cambridge University Press, 2006, ISBN 0-521-57095-6

- **1.** *Mathematical Models in the Applied Sciences*, A. C. Fowler, Cambridge University Press, 1997, ISBN 0-521-46140-5

- 2. *A First Course in Mathematical Modeling*, F. R. Giordano, M.D. Weir and W.P. Fox, 2003, Thomson, Brooks/Cole Publishers

- 3. Applied Numerical Modeling for Engineers, Donald De Cogan, Anne De Cogan, Oxford University Press, 1997

### (R18DEC51) Embedded Systems Programming (OPEN ELECTIVE I)

#### Unit 1 - Embedded OS (Linux) Internals

Linux internals: Process Management, File Management, Memory Management, I/O Management. Overview of POSIX APIs, Threads – Creation, Cancellation, POSIX Threads Inter Process Communication - Semaphore, Pipes, FIFO, Shared Memory

Kernel: Structure, Kernel Module Programming Schedulers and types of scheduling.

Interfacing: Serial, Parallel Interrupt Handling Linux Device Drivers: Character, USB, Block & Network

#### Unit 2 – Open source RTOS

Basics of RTOS: Real-time concepts, Hard Real time and Soft Real-time, Differences between General Purpose OS & RTOS, Basic architecture of an RTOS, Scheduling Systems, Inter-process communication, Performance Matric in scheduling models, Interrupt management in RTOS environment, Memory management, File systems, I/O Systems, Advantage and disadvantage of RTOS.

#### Unit 3 – Open Source RTOS Issues

POSIX standards, RTOS Issues - Selecting a Real Time Operating System, RTOS comparative study. Converting a normal Linux kernel to real time kernel, Xenomai basics.

Overview of Open source RTOS for Embedded systems (Free RTOS/ Chibios-RT) and application development.

#### Unit 4 – VxWorks / Free RTOS

VxWorks/ Free RTOS Scheduling and Task Management - Realtime scheduling, Task Creation, Intertask Communication, Pipes, Semaphore, Message Queue, Signals, Sockets, Interrupts I/O Systems - General Architecture, Device Driver Studies, Driver Module explanation, Implementation of Device Driver for a peripheral

#### Unit 5 – Case study

Cross compilers, debugging Techniques, Creation of binaries & porting stages for Embedded Development board (Beagle Bone Black, Rpi or similar), Porting an Embedded OS/ RTOS to a target board (). Testing a real time application on the board

#### **TEXT BOOKS:**

- 1. Essential Linux Device Drivers, Venkateswaran Sreekrishnan

- 2. Writing Linux Device Drivers: A Guide with Exercises, J. Cooperstein

- 3. Real Time Concepts for Embedded Systems Qing Li, Elsevier

#### **REFERENCES:**

- 1. Embedded Systems Architecture Programming and Design: Raj Kamal, Tata McGraw Hill

- 2. Embedded/Real Time Systems Concepts, Design and Programming Black Book, Prasad, KVK

- 3. Software Design for Real-Time Systems: Cooling, J E Proceedings of 17the IEEE Real-Time Systems Symposium December 4-6, 1996 Washington, DC: IEEE Computer Society

- 4. Real-time Systems Jane Liu, PH 2000

- 5. Real-Time Systems Design and Analysis: An Engineer's Handbook: Laplante, Phillip A

- 6. Structured Development for Real Time Systems V1 : Introduction and Tools: Ward, Paul T & Mellor, Stephen J

- 7. Structured Development for Real Time Systems V2 : Essential Modeling Techniques: Ward, Paul T & Mellor, Stephen J

- 8. Structured Development for Real Time Systems V3 : Implementation Modeling Techniques: Ward, Paul T & Mellor, Stephen J

- 9. Monitoring and Debugging of Distributed Real-Time Systems: TSAI, Jeffrey J P & Yang, J H

- 10. Embedded Software Primer: Simon, David E.

- 11. Embedded Systems Architecture Programming and Design: Raj Kamal, Tata McGraw

Hill

# (R18D6881) VLSI LABORATORY

#### Note:

Minimum of 10 programs from Part –I and 2 programs from Part -II are to be conducted.

Design and implementation of the following CMOS digital/analog circuits using Cadence / Mentor Graphics / Synopsys / Equivalent CAD tools. The design shall include Gate-level design, Transistor-level design, Hierarchical design, Verilog HDL/VHDL design, Logic synthesis, Simulation and verification.

# Part –I: VLSI Front End Design programs:

Programming can be done using any complier. Down load the programs on FPGA/CPLD boards and performance testing may be done using pattern generator (32 channels) and logic analyzer apart from verification by simulation with any of the front end tools.

- 1. HDL code to realize all the logic gates

- 2. Design and Simulation of adder, Serial Binary Adder, Multi Precession Adder, CarryLook Ahead Adder.

- 3. Design of 2-to-4 decoder

- 4. Design of 8-to-3 encoder (without and with parity)

- 5. Design of 8-to-1 multiplexer

- 6. Design of 4 bit binary to gray converter

- 7. Design of Multiplexer/ Demultiplexer, comparator

- 8. Design of Full adder using 3 modeling styles

- 9. Design of flip flops: SR, D, JK, T

- 10. Design of 4-bit binary, BCD counters (synchronous/ asynchronous reset) or any sequencecounter

- 11. Design of a N- bit Register of Serial- in Serial –out, Serial in parallel out, Parallel in

Serial out and Parallel in Parallel Out.

- 12. Design of Sequence Detector (Finite State Machine- Mealy and Moore Machines).

- 13. Design of 4- Bit Multiplier, Divider.

- 14. Design of ALU to Perform ADD, SUB, AND-OR, 1's and 2's Compliment, multiplication and Division.

- 15. Design of Finite State Machine.

16. Implementing the above designs on Xilinx/Altera/Cypress/equivalent based FPGA/CPLD kits

# Part -II: VLSI Back End Design programs:

Design and implementation of the following CMOS digital/analog circuits using Cadence / Mentor Graphics / Synopsys / Equivalent CAD tools. The design shall include Gate-level design/Transistor-level design/Hierarchical design/Verilog HDL or VHDL design, Logic synthesis, Simulation and verification, Scaling of CMOS Inverter for different technologies, study of secondary effects (temperature, power supply and process corners), Circuit optimization with respect to area, performance and/or power, Layout, Extraction of parasitic and back annotation, modifications in circuit parameters and layout consumption, DC/transient analysis, Verification of layouts (DRC, LVS).

- 1. Introduction to layout design rules

- 2. Layout, physical verification, placement & route for complex design, static timing Analysis, IR drops analysis and crosstalk analysis of the following:

- Basic logic gates

- CMOS inverter

- CMOS NOR/ NAND gates

- CMOS XOR and MUX gates

- CMOS 1-bit full adder

- Static / Dynamic logic circuit (register cell)

- Latch

- Pass transistorBasic logic gates

- 3. Layout of any combinational circuit (complex CMOS logic gate)- Learning about data paths

#### (R18DHS54) VALUE EDUCATION

(Audit Course I)

#### **UNIT I:**

# Values and self-development

Social values and individual attitudes, Work ethics, Indian vision of humanism, Moral and non-moral valuation. Standards and principles, Value judgements

#### **UNIT II:**

# Importance of cultivation of values

Sense of duty, Devotion, Self-reliance, Confidence, Concentration, Truthfulness, Cleanliness, Honesty, Humanity. Power of faith, National Unity, Patriotism, Love for nature, Discipline

#### **UNIT III:**

# **Personality and Behavior Development**

Soul and Scientific attitude, Positive Thinking, Integrity and discipline, Punctuality, Love and Kindness, Avoid fault Thinking, Free from anger, Dignity of labour, Universal brotherhood and religious tolerance, True friendship, Happiness Vs suffering, love for truth, Aware of self-destructive habits, Association and Cooperation, Doing best for saving nature

#### **UNIT IV:**

#### **Character and Competence**

Holy books vs Blind faith, Self-management and Good health, Science of reincarnation, Equality, Nonviolence, Humility, Role of Women, All religions and same message, Mind your Mind, Self-control, Honesty, Studying effectively

#### **TEXT BOOKS:**

1. Chakroborty, S.K. "Values and Ethics for organizations Theory and practice", Oxford University Press, New Delhi

#### (R18D6804) EMBEDDED REAL TIME OPERATING SYSTEMS

#### UNIT - I:

#### Introduction

Introduction to UNIX/LINUX, Overview of Commands, File I/O,( open, create, close, Iseek, read,write), Process Control ( fork, vfork, exit, wait, waitpid, exec.

#### UNIT - II:

#### **Real Time Operating Systems**

Brief History of OS, Defining RTOS, The Scheduler, Objects, Services, Characteristics of RTOS, Defining a Task asks States and Scheduling, Task Operations, Structure, Synchronization, **Communication and Concurrency.**

Defining Semaphores, Operations and Use, Defining Message Queue, States, Content, Storage, Operations and Use

#### UNIT - III:

# Objects, Services and I/O

Pipes, Event Registers, Signals, Other Building Blocks, Component Configuration, Basic I/O Concepts, I/O Subsystem

#### **UNIT - IV:**

#### **Exceptions, Interrupts and Timers**

Exceptions, Interrupts, Applications, Processing of Exceptions and Spurious Interrupts, Real Time Clocks, Programmable Timers, Timer Interrupt Service Routines (ISR), Soft Timers, Operations.

#### UNIT - V:

#### **Case Studies of RTOS**

RT Linux, MicroC/OS-II, Vx Works, Embedded Linux, Tiny OS, and Basic Concepts of Android OS.

#### **TEXT BOOKS:**

1. Real Time Concepts for Embedded Systems – Qing Li, Elsevier, 2011

- 1. Embedded Systems- Architecture, Programming and Design by Rajkamal, 2007, TMH.

- 2. Advanced UNIX Programming, Richard Stevens

- 3. Embedded Linux: Hardware, Software and Interfacing Dr. Craig Hollabaugh

# (R18D6805) CMOS MIXED SIGNAL CIRCUIT DESIGN

#### UNIT -I:

#### **Switched Capacitor Circuits:**

Introduction to Switched Capacitor circuits- basic building blocks, Operation and Analysis, Non-ideal effects in switched capacitor circuits, Switched capacitor integrators first order filters, Switch sharing, biquad filters.

#### UNIT -II:

#### Phased Lock Loop (PLL):

Basic PLL topology, Dynamics of simple PLL, Charge pump PLLs-Lock acquisition, Phase/Frequency detector and charge pump, Basic charge pump PLL, Non-ideal effects in PLLs-PFD/CP non-idealities, Jitter in PLLs, Delay locked loops, applications

#### UNIT -III:

# **Data Converter Fundamentals:**

DC and dynamic specifications, Quantization noise, Nyquist rate D/A converters- Decoder based converters, Binary-Scaled converters, Thermometer-code converters, Hybrid converters

#### **UNIT-IV:**

# Nyquist Rate A/D Converters:

Successive approximation converters, Flash converter, Two-step A/D converters, Interpolating A/D converters, Folding A/D converters, Pipelined A/D converters, Time-interleaved converters.

#### UNIT -V:

# **Oversampling Converters:**

Noise shaping modulators, Decimating filters and interpolating filters, Higher order modulators, Delta sigma modulators with multibit quantizers, Delta sigma D/A

#### **TEXT BOOKS:**

- 1. Design of Analog CMOS Integrated Circuits- Behzad Razavi, TMH Edition, 2002

- 2. CMOS Analog Circuit Design Philip E. Allen and Douglas R. Holberg, Oxford University Press,International Second Edition/Indian Edition, 2010.

- 3. Analog Integrated Circuit Design- David A. Johns, Ken Martin, Wiley Student Edition, 2013

- 1. CMOS Integrated Analog-to- Digital and Digital-to-Analog converters-Rudy Van De Plassche, Kluwer Academic Publishers, 2003

- 2. Understanding Delta-Sigma Data converters-Richard Schreier, Wiley Interscience, 2005.

- 3. CMOS Mixed-Signal Circuit Design R. Jacob Baker, Wiley Interscience, 2009.

#### (R18D6806) LOW POWER VLSI DESIGN

#### UNIT -I:

#### **Fundamentals:**

Need for Low Power Circuit Design, Sources of Power Dissipation – Switching Power Dissipation, Short Circuit Power Dissipation, Leakage Power Dissipation, Glitching Power Dissipation, ShortChannel Effects – Drain Induced Barrier Lowering and Punch Through, Surface Scattering, VelocitySaturation, Impact Ionization, Hot Electron Effect.

# UNIT -II:

### **Low-Power Design Approaches:**

Low-Power Design through Voltage Scaling – VTCMOS circuits, MTCMOS circuits, Architectural Level Approach –Pipelining and Parallel Processing Approaches.

# **Switched Capacitance Minimization Approaches:**

System Level Measures, Circuit Level Measures, Mask level Measures.

#### UNIT -III:

### **Low-Voltage Low-Power Adders:**

Introduction, Standard Adder Cells, CMOS Adder's Architectures – Ripple Carry Adders, Carry Look-Ahead Adders, Carry Select Adders, Carry Save Adders, Low-Voltage Low-Power Design Techniques—Trends of Technology and Power Supply Voltage, Low-Voltage Low-Power Logic Styles.

#### UNIT -IV:

# **Low-Voltage Low-Power Multipliers:**

Introduction, Overview of Multiplication, Types of Multiplier Architectures, Braun Multiplier, Baugh-Wooley Multiplier, Booth Multiplier, Introduction to Wallace Tree Multiplier.

#### UNIT -V:

# **Low-Voltage Low-Power Memories:**

Basics of ROM, Low-Power ROM Technology, Future Trend and Development of ROMs, Basics of SRAM, Memory Cell, Precharge and Equalization Circuit, Low-Power SRAM Technologies, Basics of DRAM, Self-Refresh Circuit, Future Trend and Development of DRAM.

#### **TEXT BOOKS:**

- 1. CMOS Digital Integrated Circuits Analysis and Design Sung-Mo Kang, Yusuf Leblebici, TMH, 2011.

- 2. Low-Voltage, Low-Power VLSI Subsystems Kiat-Seng Yeo, Kaushik Roy, TMH Professional Engineering.

- 1. Introduction to VLSI Systems: A Logic, Circuit and System Perspective Ming-BO Lin, CRC Press, 2011

- 2. Low Power CMOS Design AnanthaChandrakasan, IEEE Press/Wiley International, 1998.

- 3. Low Power CMOS VLSI Circuit Design Kaushik Roy, Sharat C. Prasad, John Wiley & Sons, 2000.

- 4. Practical Low Power Digital VLSI Design Gary K. Yeap, Kluwer Academic Press, 2002.

- 5. Low Power CMOS VLSI Circuit Design A. Bellamour, M. I. Elamasri, Kluwer Academic Press, 1995.

- 6. Leakage in Nanometer CMOS Technologies Siva G. Narendran, AnathaChandrakasan, Springer, 2005.

# (R18D6813) ADHOC –WIRELESS NETWORKS (ELECTIVE -III)

#### UNIT -I:

**Wireless LANS and PANS:** Introduction, Fundamentals of WLANS, IEEE 802.11 Standards, HIPERLAN Standard, Bluetooth, Home RF.

AD HOC Wireless Networks: Introduction, Issues in Ad Hoc Wireless Networks.

#### UNIT -II:

**MAC Protocols:** Introduction, Issues in Designing a MAC protocol for Ad Hoc Wireless Networks, Design goals of a MAC Protocol for Ad Hoc Wireless Networks, Classifications of MAC Protocols, Contention - Based Protocols, Contention - Based Protocols with reservation Mechanisms, Contention - Based MAC Protocols with Scheduling Mechanisms, MAC Protocols that use Directional Antennas, Other MAC Protocols.

#### **UNIT-III:**

**Routing Protocols:** Introduction, Issues in Designing a Routing Protocol for Ad Hoc Wireless Networks, Classification of Routing Protocols, Table –Driven Routing Protocols, On – Demand Routing Protocols, Hybrid Routing Protocols, Routing Protocols with Efficient Flooding Mechanisms, Hierarchical Routing Protocols, Power – Aware Routing Protocols.

#### UNIT-IV:

**Transport Layer Protocols:** Introduction, Issues in Designing a Transport Layer Protocol for Ad Hoc Wireless Networks, Design Goals of a Transport Layer Protocol for Ad Hoc Wireless Networks, Classification of Transport Layer Solutions, TCP Over Ad Hoc Wireless Networks, Other Transport Layer Protocol for Ad Hoc Wireless Networks.

#### UNIT -V:

**Wireless Sensor Networks:** Introduction, Sensor Network Architecture, Data Dissemination, Data Gathering, MAC Protocols for Sensor Networks, Location Discovery, Quality of a Sensor Network, Evolving Standards, Other Issues.

#### **TEXT BOOKS:**

- 1. Ad Hoc Wireless Networks: Architectures and Protocols C. Siva Ram Murthy and B.S.Manoj, 2004, PHI.

- 2. Wireless Ad- hoc and Sensor Networks: Protocols, Performance and Control Jagannathan Sarangapani, CRC Press.

- 1. Ad- Hoc Mobile Wireless Networks: Protocols & Systems, C.K. Toh , 1st Ed. Pearson Education.

- 2. Wireless Sensor Networks C. S. Raghavendra, Krishna M. Sivalingam, 2004, Springer.

# (R18D6814)SOC DESIGN (ELECTIVE – III)

#### **UNIT I:**

#### **ASIC**

Overview of ASIC types, design strategies, CISC, RISC and NISC approaches for SOC architectural issues and its impact on SoC design methodologies, Application Specific Instruction Processor (ASIP) concepts.

#### **UNIT 2:**

#### NISC

NISC Control Words methodology, NISC Applications and Advantages, Architecture Description Languages (ADL) for design and verification of Application Specific Instruction set Processors (ASIP), No-Instruction-Set-computer (NISC)- design flow, modeling NISC architectures and systems, use of Generic Netlist Representation - A formal language for specification, compilation and synthesis of embedded processors.

#### UNIT III:

#### Simulation

Different simulation modes, behavioural, functional, static timing, gate level, switch level, transistor/circuit simulation, design of verification vectors, Low power FPGA, Reconfigurable systems, SoC related modeling of data path design and control logic, Minimization of interconnects impact, clock tree design issues.

#### **UNIT IV:**

# Low power SoC design / Digital system

Design synergy, Low power system perspective- power gating, clock gating, adaptive voltage scaling (AVS), Static voltage scaling, Dynamic clock frequency and voltage scaling (DCFS), building block optimization, building block memory, power down techniques, power consumption verification.

#### **UNIT V:**

### **Synthesis**

Role and Concept of graph theory and its relevance to synthesizable constructs, Walks, trails paths, connectivity, components, mapping/visualization, nodal and admittance graph, Technology independent and technology dependent approaches for synthesis, optimization constraints, Synthesis report analysis, Single core and Multi core systems, dark silicon issues, HDL coding techniques for minimization of power consumption, Fault tolerant designs. Case study for overview of cellular phone design with emphasis on area optimization, speed improvement and power minimization.

- 1.Hubert Kaeslin, "Digital Integrated Circuit Design: From VLSI Architectures to CMOS Fabrication", Cambridge University Press, 2008.

- 2. B. Al Hashimi, "System on chip-Next generation electronics", The IET, 2006

- 3. RochitRajsuman, "System-on- a-chip: Design and test", Advantest America R & D Center, 2000

- 4. P Mishra and N Dutt, "Processor Description Languages", Morgan Kaufmann, 2008

- 5. Michael J. Flynn and Wayne Luk, "Computer System Design: System-on-Chip". Wiley, 2011

#### ( R18D6815)MEMORY TECHNOLOGIES

(ELECTIVE - III)

#### UNIT I:

#### **Random Access Memory Technologies**

Static Random Access Memories (SRAMs), SRAM Cell Structures, MOS SRAM Architecture, MOS SRAM Cell and Peripheral Circuit, Bipolar SRAM, Advanced SRAM Architectures, Application Specific SRAMs.

#### Unit II:

#### **DRAM DESIGN**

DRAMs, MOS DRAM Cell, BiCMOS DRAM, Error Failures in DRAM, Advanced DRAM Design and Architecture, Application Specific DRAMs.SRAM and DRAM Memory controllers.

#### Unit III:

#### **Non-Volatile Memories**

Masked ROMs, PROMs, Bipolar & CMOS PROM, EEPROMs, Floating Gate EPROM Cell, OTP EPROM, EEPROMs, Non-volatile SRAM, Flash Memories.

#### **Unit IV:**

#### **Semiconductor Memory Reliability and Radiation Effects**

General Reliability Issues, RAM Failure Modes and Mechanism, Nonvolatile Memory, Radiation Effects, SEP, Radiation Hardening Techniques. Process and Design Issues, Radiation Hardened Memory Characteristics, Radiation

#### Unit V:

# **Advanced Memory Technologies and High-density Memory Packing Technologies**

Ferroelectric Random Access Memories (FRAMs), Gallium Arsenide (GaAs) FRAMs, Analog Memories, Magneto Resistive Random Access Memories (MRAMs), Experimental Memory Devices, Memory Hybrids (2D & 3D), Memory Stacks, Memory Testing and Reliability Issues, Memory Cards, High Density Memory Packaging

- 1. Ashok K Sharma, "Advanced Semiconductor Memories: Architectures, Designs and Applications", Wiley Interscience

- 2. Kiyoo Itoh, "VLSI memory chip design", Springer International Edition

- 3. Ashok K Sharma," Semiconductor Memories: Technology, Testing and Reliability, PHI

# (R18D6816)PHYSICAL DESIGN AUTOMATION (ELECTIVE- IV)

#### UNIT I:

# **Introduction to VLSI Design Methodologies**

Design and Fabrication of VLSI Devices, Fabrication Process and its impact on Design.

#### **UNIT II:**

# **VLSI** design automation tools

Data structures and basic algorithms, graph theory and computational complexity, tractable and intractable problems.

#### **UNIT III:**

#### General purpose methods for combinational optimization

Partitioning, floor planning and pin assignment, placement, routing. Concepts and Algorithms Modeling: Gate Level Modeling and Simulation, Switch level modeling and simulation, Basic issues and Terminology, Binary – Decision diagram, Two – Level Logic Synthesis.

Hardware Models: Internal representation of the input algorithm, Allocation, Assignment and Scheduling, Some Scheduling Algorithms, Some aspects of Assignment problem, High – level Transformations.

#### Unit 4:

Simulation

Logic synthesis, verification, high level Synthesis. FPGA technologies: Physical Design cycle for FPGA's partitioning and routing for segmented and staggered models

#### **UNIT V:**

### **MCM** technologies

MCM physical design cycle, Partitioning, Placement – Chip array based and full custom approaches, Routing –Maze routing, Multiple stage routing, Topologic routing, Integrated Pin – Distribution and routing, routing and programmable MCM's.

- 1. S.H.Gerez, "Algorithms for VLSI Design Automation", John Wiley 1999.

- 2. Naveed Sherwani, "Algorithms for VLSI Physical Design Automation" 3rd edition, Springer International Edition. REFERENCES 1. Hill & Peterson, "Computer Aided Logical Design with Emphasis on VLSI" Wiley,1993 2. Wayne Wolf, "Modern VLSI Design: Systems on silicon" Pearson Education Asia, 2nd Edition.

# (R18D6817)COMMUNICATION BUSES AND INTERFACES (ELECTIVE- IV)

#### Unit 1:

Serial Buses: Physical interface, Data and Control signals, features

#### Unit 2:

Limitations and applications of RS232, RS485, I2C, SPI

#### Unit 3:

CAN Architecture, Data transmission, Layers, Frame formats, applications

#### Unit 4:

PCIe - Revisions, Configuration space, Hardware protocols, applications

#### Unit 5:

USB - Transfer types, enumeration, Descriptor types and contents, Device driver Data Streaming Serial Communication Protocol - Serial Front Panel Data Port (SFPDP) using fibre optic and copper cable

- 1. Jan Axelson, "Serial Port Complete COM Ports, USB Virtual Com Ports, and Ports for Embedded Systems", Lakeview Research, 2nd Edition

- 2.Jan Axelson, "USB Complete", Penram Publications

- 3. Mike Jackson, Ravi Budruk, "PCI Express Technology", Mindshare Press

- 4. Wilfried Voss, "A Comprehensible Guide to Controller Area Network", Copperhill Media Corporation, 2nd Edition, 2005.

- 5. Serial Front Panel Draft Standard VITA 17.1 200x

# (R18D6818) MULTIMEDIA AND SIGNAL CODING (ELECTIVE-IV)

#### UNIT-I:

#### Introduction to Multimedia

Multimedia, World Wide Web, Overview of Multimedia Tools, Multimedia Authoring, Graphics/ Image Data Types, and File Formats.

Color in Image and Video: Color Science – Image Formation, Camera Systems, Gamma Correction, Color Matching Functions, CIE Chromaticity Diagram, Color Monitor Specifications, Out-of-Gamut Colors, White Point Correction, XYZ to RGB Transform, Transform with Gamma Correction, L\*A\*B\* Color Model. Color Models in Images – RGB Color Model for CRT Displays, Subtractive Color: CMY Color Model, Transformation from RGB to CMY, Under Color Removal: CMYK System, Printer Gamuts, Color Models in Video – Video Color Transforms, YUV Color Model, YIQ Color Model, Ycbcr Color Model.

#### UNIT-II:

Video Concepts: Types of Video Signals, Analog Video, Digital Video.

Audio Concepts: Digitization of Sound, Quantization and Transmission of Audio.

#### **UNIT-III:**

# **Compression Algorithms**

**Lossless Compression Algorithms:** Run Length Coding, Variable Length Coding, Arithmetic Coding, Lossless JPEG, Image Compression.

**Lossy Image Compression Algorithms:** Transform Coding: KLT And DCT Coding, Wavelet Based Coding.

Image Compression Standards: JPEG and JPEG2000.

#### UNIT-IV:

#### **Video Compression Techniques**

Introduction to Video Compression, Video Compression Based on Motion Compensation, Search for Motion Vectors, H.261- Intra-Frame and InterFrame Coding, Quantization, Encoder and Decoder, Overview of MPEG1 and MPEG2.

#### **UNIT-V:**

Audio, Channel Vocoder, Formant Vocoder, Linear Predictive Coding, CELP, Hybrid Excitation Vocoders, MPEG Audio – MPEG Layers, MPEG Audio Strategy, MPEG Audio Compression Algorithms, MPEG-2 AAC, MPEG-4 Audio.

# **TEXT BOOKS:**

- 1. Fundamentals of Multimedia Ze- Nian Li, Mark S. Drew, PHI, 2010.

- 2. Multimedia Signals & Systems Mrinal Kr. Mandal Springer International Edition 1st Edition, 2009.

#### **REFERENCE BOOKS:**

1. Multimedia Communication Systems – Techniques, Stds & Netwroks K.R. Rao, Zorans. Bojkoric, Dragorad A. Milovanovic, 1st Edition, 2002.

| 2.            | Fundamentals of Multimedia Ze- Nian Li, Mark S.Drew, Pearson Education (LPE), 1st Edition, 2009.                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|               | Multimedia Systems John F. Koegel Bufond Pearson Education (LPE), 1st Edition, 2003. Digital Video Processing – A. Murat Tekalp, PHI, 1996. |

| Video<br>2002 | Processing and Communications – Yaowang, Jorn Ostermann, Ya-QinZhang, Pearson,                                                              |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

|               |                                                                                                                                             |

# (R18DME54) Composite Materials (OPEN ELECTIVE II)

**UNIT–I: Introduction:** Definition – Classification and characteristics of Composite materials, Advantages and application of composites. Functional requirements of reinforcement and matrix, Effect of reinforcement (size, shape, distribution, volume fraction) on overall composite performance.

**UNIT – II**: **Reinforcements:** Preparation-layup, curing, properties and applications of glass fibers, carbon fibers, Kevlar fibers and Boron fibers. Properties and applications of whiskers, particle reinforcements. Mechanical Behavior of composites: Rule of mixtures, Inverse rule of mixtures, Isostrain and Isostress conditions.

**UNIT** – **III: Manufacturing of Metal Matrix Composites:** Casting – Solid State diffusion technique, Cladding – Hot isostatic pressing. Properties and applications. Manufacturing of Ceramic Matrix Composites: Liquid Metal Infiltration – Liquid phase sintering. Manufacturing of Carbon – Carbon composites: Knitting, Braiding, Weaving. Properties and applications.

**UNIT-IV: Manufacturing of Polymer Matrix Composites:** Preparation of Moulding compounds and prepregs – hand layup method – Autoclave method – Filament winding method – Compression moulding – Reaction injection, Moulding, Properties and applications.

**UNIT – V: Strength:**Laminar Failure Criteria-strength ratio, maximum stress criteria, maximum strain criteria, interacting failure criteria, hygrothermal failure. Laminate first play failure-insight strength; Laminate strength-ply discount truncated maximum strain criterion; strength design using caplet plots; stress concentrations.

#### **TEXT BOOKS:**